- 您现在的位置:买卖IC网 > Sheet目录3832 > AT87C54X2-3CSUL (Atmel)IC 8051 MCU 16K EPROM 40DIP

39

4431E–8051–04/06

AT/TS8xC54/8X2

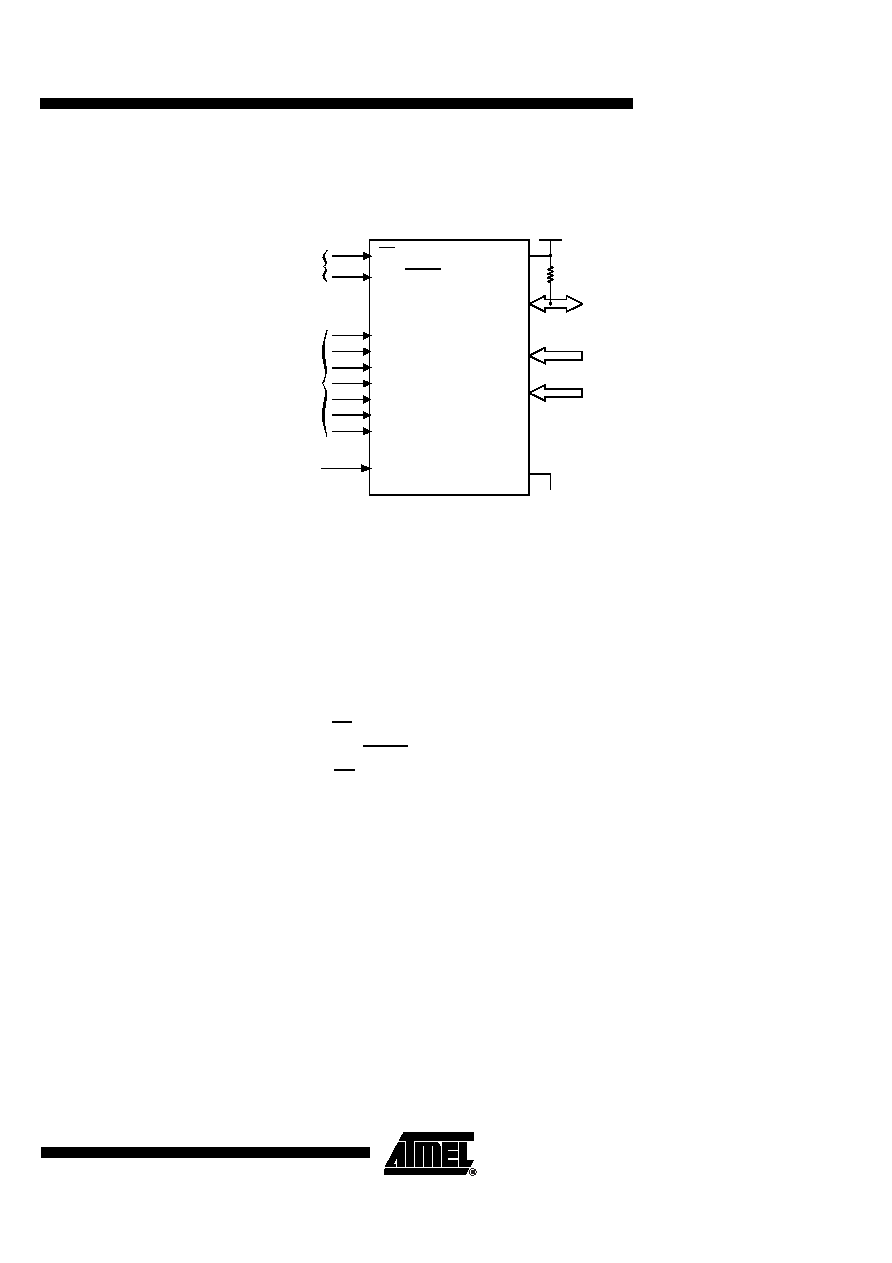

Figure 17-1. Set-Up Modes Configuration

17.3.3

Programming Algorithm

The Improved Quick Pulse algorithm is based on the Quick Pulse algorithm and decreases the

number of pulses applied during byte programming from 25 to 1.

To program the TS80C54/58X2 the following sequence must be exercised:

Step 1: Activate the combination of control signals.

Step 2: Input the valid address on the address lines.

Step 3: Input the appropriate data on the data lines.

Step 4: Raise EA/VPP from VCC to VPP (typical 12.75V).

Step 5: Pulse ALE/PROG once.

Step 6: Lower EA/VPP from VPP to VCC

Repeat step 2 through 6 changing the address and data for the entire array or until the end of

the object file is reached (See Figure 17-2.).

17.3.4

Verify algorithm

Code array verify must be done after each byte or block of bytes is programmed. In either case,

a com plete verify of th e p rog ra mm ed array wil l ensure rel iable program m ing of the

TS87C54/58X2.

P 2.7 is used to enable data output.

To verify the TS87C54/58X2 code the following sequence must be exercised:

Step 1: Activate the combination of program and control signals.

Step 2: Input the valid address on the address lines.

Step 3: Read data on the data lines.

Repeat step 2 through 3 changing the address for the entire array verification (See Figure 17-2.)

+5V

VCC

P0.0-P0.7

P1.0-P1.7

P2.0-P2.5,

VSS

GND

D0-D7

A0-A7

A8-A14

RST

EA/VPP

ALE/PROG

PSEN

P2.6

P2.7

P3.3

P3.7

P3.6

XTAL1

4 to 6 MHz

CON T RO L

SIGNALS*

PR O G R AM

SIGNALS*

* See Table 31. for proper value on these inputs

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT87C52X2-SLSUM

IC 8051 MCU 8K OTP 40MHZ 44PLCC

PIC16LF76-I/SP

IC PIC MCU FLASH 8KX14 28DIP

PIC18LF2431-I/SO

IC MCU FLASH 8KX16 28SOIC

AT87C52X2-SLSUL

IC 8051 MCU 8K OTP 30MHZ 44PLCC

PIC32MX420F032H-40V/PT

IC MCU 32BIT 32KB FLASH 64TQFP

PIC32MX320F064H-40V/PT

IC MCU 32BIT 64KB FLASH 64TQFP

DSPIC33FJ64GP306A-I/PT

IC DSPIC MCU/DSP 64K 64-TQFP

AT87C52X2-RLTUM

IC 8051 MCU 8K OTP 40MHZ 44VQFP

相关代理商/技术参数

AT87C54X2-3CSUM

功能描述:8位微控制器 -MCU MICRO OTP RB/16K 40MHZ 5V C RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C54X2-3CSUV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller 16/32 Kbytes ROM/OTP

AT87C54X2-RLTUL

功能描述:8位微控制器 -MCU OTP C54/16K 40MHZ 3V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C54X2-RLTUM

功能描述:8位微控制器 -MCU OTP C54B/16K 40MHZ 5V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C54X2-RLTUV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller 16/32 Kbytes ROM/OTP

AT87C54X2-SLRUM

功能描述:8位微控制器 -MCU 16K 40MHz RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C54X2-SLSUL

功能描述:8位微控制器 -MCU OTP C54/16K 40MHZ 3V COM TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C54X2-SLSUM

功能描述:8位微控制器 -MCU OTP C54/16K 40MHZ 5V IND TEMP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT